Strict equal to: true if the operands are equal and of the same type $display ("Original data = 'd%0d or 'b%0b", data, data) įor (i = 0 i > %0d = 'b%b", i, data > i) Not equal to: true if the operands are not equal This operator will combine a bit in one operand with its corresponding bit in the other operand to calculate a single bit result. The logical negation (!) operator will convert a non-zero or true operand into 0 and a zero or false operand into 1, while an X will remain as an X.Ĭonverts non-zero value to zero, and vice versaĭata1 = 45 data2 = 9 $display ("Result of data1(%0d) & data2(%0d) : %0d", data1, data2, data1 & data2) ĭata1 = 0 data2 = 4 $display ("Result of data1(%0d) & data2(%0d) : %0d", data1, data2, data1 & data2) ĭata1 = 'dx data2 = 3 $display ("Result of data1(%0d) & data2(%0d) : %0d", data1, data2, data1 & data2) ĭata1 = 'b101z data2 = 5 $display ("Result of data1(%0d) & data2(%0d) : %0d", data1, data2, data1 & data2) ĭata1 = 45 data2 = 9 $display ("Result of data1(%0d) || data2(%0d) : %0d", data1, data2, data1 || data2) ĭata1 = 0 data2 = 4 $display ("Result of data1(%0d) || data2(%0d) : %0d", data1, data2, data1 || data2) ĭata1 = 'dx data2 = 3 $display ("Result of data1(%0d) || data2(%0d) : %0d", data1, data2, data1 || data2) ĭata1 = 'b101z data2 = 5 $display ("Result of data1(%0d) || data2(%0d) : %0d", data1, data2, data1 || data2) ĭata1 = 4 $display ("Result of !data1(%0d) : %0d", data1, !data1) ĭata1 = 0 $display ("Result of !data1(%0d) : %0d", data1, !data1) If either of the operands is X, then the result will be X as well.

The result of a logical or (||) is 1 or true when either of its operands are true or non-zero. The result of a logical and (&) is 1 or true when both its operands are true or non-zero.

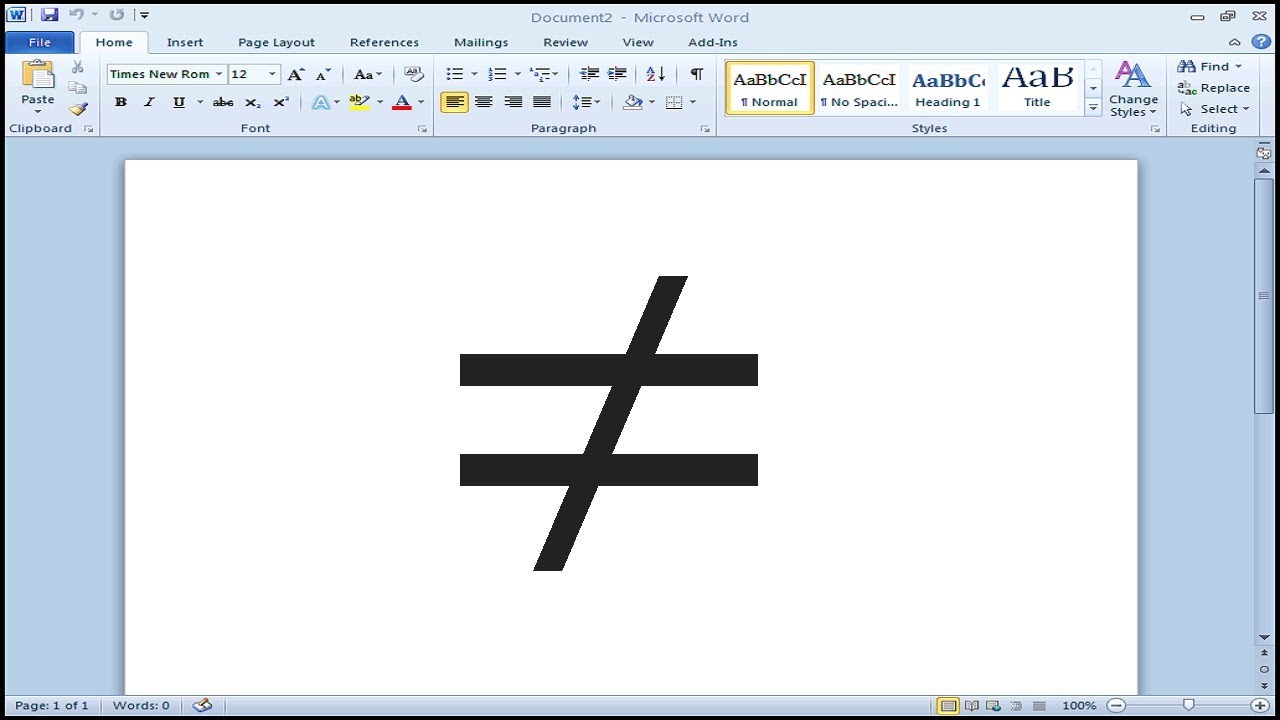

If either of the operands of logical-equality (=) or logical-inequality (!=) is X or Z, then the result will be X. $display ("Result for data1 data2 : %0d", data1 > data2) Įquality operators have the same precedence amongst them and are lower in precedence than relational operators. $display ("Result for data1 >= data2 : %0d", data1 >= data2) Relational operators have a lower precedence than arithmetic operators and all relational operators have the same precedence. If either of the operands is X or Z, then the result will be X.

Ncsim: *W,RNQUIE: Simulation is complete.Īn expression with the relational operator will result in a 1 if the expression is evaluated to be true, and 0 if it is false.

Logic not equal symbol generator#

Introduction What is Verilog? Introduction to Verilog Chip Design Flow Chip Abstraction Layers Data Types Verilog Syntax Verilog Data types Verilog Scalar/Vector Verilog Arrays Building Blocks Verilog Module Verilog Port Verilog Module Instantiations Verilog assign statements Verilog assign examples Verilog Operators Verilog Concatenation Verilog always block Combo Logic with always Sequential Logic with always Verilog initial block Verilog in a nutshell Verilog generate Verilog Sequence Detector Verilog Pattern Detector Behavioral modeling Verilog Block Statements Verilog Assignment Types Verilog Blocking/Non-blocking Verilog Control Flow Verilog for Loop Verilog case Statement Verilog Functions Verilog Tasks Verilog Parameters Verilog `ifdef `elsif Verilog Delay Control Verilog Inter/Intra Delay Verilog Hierarchical Reference Gate/Switch modeling Gate Level Modeling Gate Level Examples Gate Delays Switch Level Modeling User-Defined Primitives Simulation Verilog Simulation Basics Verilog Timescale Verilog Scheduling Regions Verilog Clock Generator System Tasks and Functions Verilog Display tasks Verilog Math Functions Verilog Timeformat Verilog Timescale Scope Verilog File Operations Code Examples Hello World! Flops and Latches JK Flip-Flop D Flip-Flop T Flip-Flop D Latch Counters 4-bit counter Ripple Counter Straight Ring Counter Johnson Counter Mod-N Counter Gray Counter Misc n-bit Shift Register Priority Encoder 4x1 multiplexer Full adder Single Port RAMĪn example of how arithmetic operators are used is given below.

0 kommentar(er)

0 kommentar(er)